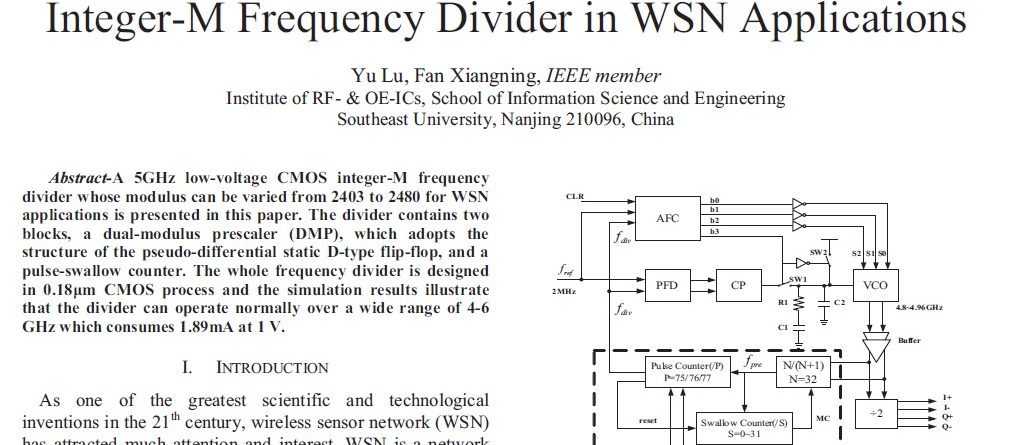

Design of a Low-Voltage High-Speed CMOS Integer-M Frequency Divider in WSN Applications

از لینک زیر میتوانید مقاله Design of a Low-Voltage High-Speed CMOS Integer-M Frequency Divider in WSN Applications‚ همراه با گزارش فارسی ترجمه و فایل شبیه سازی hspice آنرا خریداری کنید . این مقاله مربوط به سال 2012 ieee میباشد که اطلاعات آن را در ادامه میتوانید مشاهده نمایید .

چکیده Frequency Divider

در این مقاله یک مقسم فرکانسی صحیح 5GHz CMOS ولتاژ پایین برای کاربردهای WSN که از 2403 تا 2480 تغییر می کند ، ارائه شده است . مقسم شامل دو بلوک است ، prescaler دو ماژوله (DMP) که از یک فلیپ فلاپ استاتیک نوع D شبه تفاضلی استفاده می کند و یک شمارنده -swallow pulse . مقسم فرکانس در پروسه 0.18µm CMOS طراحی می شود و نتایج شبیه سازی نشان می دهد که مقسم معمولا” می تواند در سرتاسر پهنای باند 4-6GHz با مصرف 1.89mA در 1V کار کند .

نتایج شبیه سازی نشان می دهد مقسم فرکانسی صحیح می تواند از 4GHz تا 6GHz عمل کند و تلفات توانی در حدود 1.89mW می باشد و تحت شرایط PVT ، می تواند بطور نرمال کار کند

A 5GHz low-voltage CMOS integer-M frequency divider whose modulus can be varied from 2403 to 2480 for WSN applications is presented in this paper. The divider contains two blocks, a dual-modulus prescaler (DMP), which adopts the structure of the pseudo-differential static D-type flip-flop, and a pulse-swallow counter. The whole frequency divider is designed in 0.18μm CMOS process and the simulation results illustrate that the divider can operate normally over a wide range of 4-6 GHz which consumes 1.89mA at 1 V.

Published in:

High Speed Intelligent Communication Forum (HSIC), 2012 4th International

Author(s)

Date of Conference:

10-11 May 2012

- Page(s):

- 1 – 4

- E-ISBN :

- 978-1-4673-0676-8

- Print ISBN:

- 978-1-4673-0678-2

- INSPEC Accession Number:

- 12787434

- Conference Location :

- Nanjing, Jiangsu

- DOI:

- 10.1109/HSIC.2012.6213023

- Publisher:

- IEEE

دیدگاهتان را بنویسید