Low-Power Pulse-Triggered Flip-Flop Design Based on a Signal Feed-Through Scheme

از لینک زیر مقاله Low-Power Pulse-Triggered Flip-Flop Design Based on a Signal Feed-Through Scheme به همراه ترجمه و فایل شبیه سازی hspice انرا میتوانید دریافت نمایید .

Abstract:

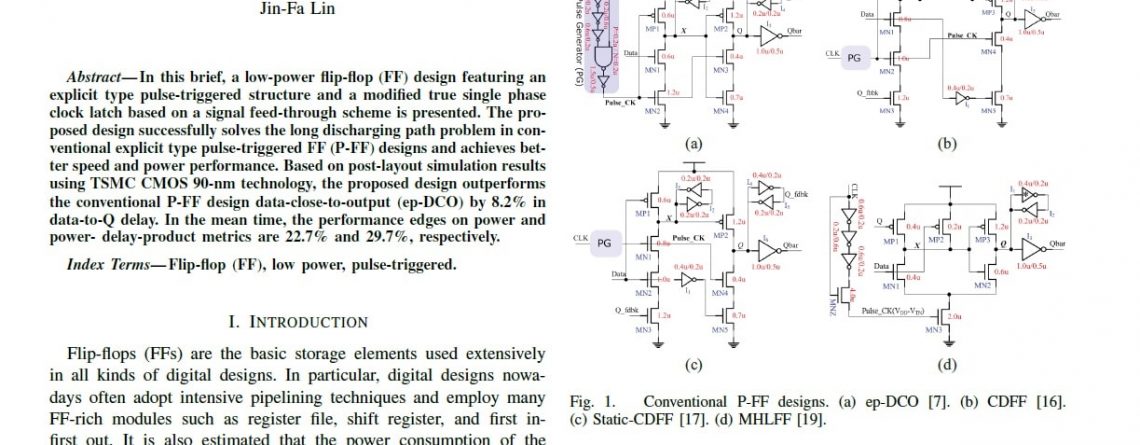

In this brief, a low-power flip-flop (FF) design featuring an explicit type pulse-triggered structure and a modified true single phase clock latch based on a signal feed-through scheme is presented. The proposed design successfully solves the long discharging path problem in conventional explicit type pulse-triggered FF (P-FF) designs and achieves better speed and power performance. Based on post-layout simulation results using TSMC CMOS 90-nm technology, the proposed design outperforms the conventional P-FF design data-close-to-output (ep-DCO) by 8.2% in data-to-Q delay. In the mean time, the performance edges on power and power- delay-product metrics are 22.7% and 29.7%, respectively.

Published in: IEEE Transactions on Very Large Scale Integration (VLSI) Systems ( Volume: 22, Issue: 1, Jan. 2014 )

Page(s): 181 – 185

Date of Publication: 17 January 2013

ISSN Information:

INSPEC Accession Number: 13991728

Publisher: IEEE

Sponsored by: IEEE Circuits and Systems Society

IEEE Computer Society

IEEE Solid-State Circuits Society

IEEE Computer Society

IEEE Solid-State Circuits Society

دیدگاهتان را بنویسید