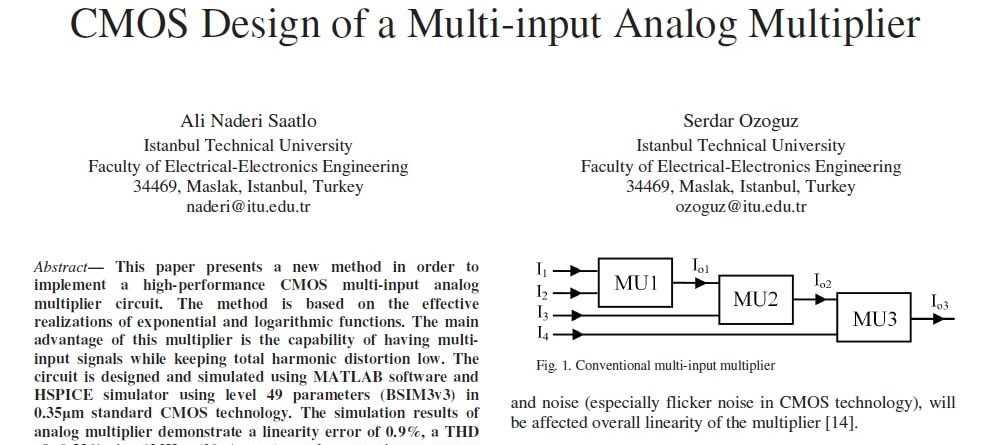

CMOS Design of a Multi-input Analog Multiplier

از لینک زیر مقاله CMOS Design of a Multi-input Analog Multiplier به همراه فایل شبیه سازی Hspice انرا میتوانید دریافت نمایید .

Abstract:

This paper presents a new method in order to implement a high-performance CMOS multi-input analog multiplier circuit. The method is based on the effective realizations of exponential and logarithmic functions. The main advantage of this multiplier is the capability of having multiinput signals while keeping total harmonic distortion low. The circuit is designed and simulated using MATLAB software and HSPICE simulator using level 49 parameters (BSIM3v3) in 0.35 micrometer standard CMOS technology. The simulation results of analog multiplier demonstrate a linearity error of 0.9%, a THD of 0.33% in 1 MHz (20 muA p-p), and a maximum power consumption of 0.89 mW. Keywords – component; CMOS; analog; current mode; multiinput; multiplier circuit

دیدگاهتان را بنویسید